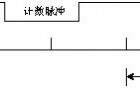

实实在在的工作场景中,触发器的运作状态不仅仅要受到触发输入讯号的制约,还需遵循特定的节奏来进行操作。为了实现这一点,我们需要增设一个时钟控制端口。

1. 电平触发SR触发器

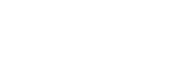

同步RS触发器的时钟脉冲CP仅仅负责控制触发器状态允许转变的时间段,而触发器最终会呈现出0态或者1态,抑或是维持原状,这完全取决于输入端R、S的状态。

使用SD’或RD’来对触发器进行置位或复位的操作,应该选择在CLK=0的时刻进行,否则在SD’或RD’恢复至高电平之后,原先设定的状态未必能够被完整地保留下来。

电平触发模式的运作特征主要包括以下几点:

当CP处于1的状态时,输入信号的任何变动都会立即影响到输出端Q和Q′的状态;

当CP为1时,如果输入信号频繁发生变化,那么触发器的状态也会随之多次翻转,因此这种方式的抗干扰性能较弱,例如当S信号遭受微小的干扰(正脉冲)时,Q可能会翻转为1状态,无法继续保持0状态;

在CP为1的时段内出现的多次翻转现象,我们称之为“空翻”,这是时序电路中的一种潜在风险;

当CP为0时,输出状态将保持稳定不变。

2. D锁存器

特性方程:Q*=D 特点:Q*始终跟随D信号的变化